MEMS器件封裝無鉛錫膏深圳福英達分享:MEMS 器件低應力封裝技術

MEMS器件封裝無鉛超微錫膏深圳福英達分享:MEMS 器件低應力封裝技術

錫膏_焊錫膏_超微焊料_助焊膏生產商-深圳福英達是一家集錫膏、錫膠及合金焊粉產、銷、研與服務于一體的綜合型錫膏供應商, 是工信部焊錫粉標準制定主導單位,產品涵蓋超微無鉛印刷錫膏,超微無鉛點膠錫膏,超微無鉛噴印錫膏,超微無鉛針轉移錫膏,超微無鉛免洗焊錫膏,超微無鉛水洗錫膏,高溫焊錫膏,中高溫焊錫膏,低溫焊錫膏,7號錫膏、8號錫膏,低溫超微錫膠,中高溫錫膠,各向異性導電膠,金錫錫膏,金錫錫粉,多次回流錫膏,激光錫膏,微間距助焊膠,高溫無鉛錫膏,低溫錫鉍銀錫膏,低溫高可靠性錫膏,無鉛焊膏錫鉍銀錫膏/膠,SAC305錫膏,低溫高可靠性錫膏&錫膠,無銀&錫銅錫膏,超微焊粉,Low alpha無鉛焊料,Low alpha高鉛焊料,SMT粉,定制焊料。擁有從合金焊粉到應用產品的完整產品線,可制造T2-T10全尺寸超微合金焊粉的電子級封裝材料。

摘要:封裝是微機電系統(micro-electro-mechanical system, MEMS)研發過程中的最重要的環節之一。封裝決定了MEMS 器件的可靠性以及成本,是MEMS 器件實用化和商業化的關鍵。然而,封裝過程中引入的殘余應力會造成MEMS 器件輸出信號的偏移,同時封裝應力隨時間逐漸變化,嚴重影響MEMS 器件的可靠性以及長期穩定性。因此,降低封裝應力是實現MEMS 器件高性能和高穩定性的關鍵要素。簡要分析了芯片級封裝過程中MEMS 器件封裝應力產生的機理,詳細介紹了目前國內外降低應力封裝技術和方法,并對于MEMS 器件低應力封裝技術作出了總結和展望。

關鍵詞:MEMS;傳感器;低應力封裝;可靠性;長期穩定性

0 引言

微機電系統(micro-electro-mechanical systems,MEMS)是一種將電和機械集成的微器件或微系統。MEMS 沿用集成電路(integrated circuit,IC)的微米/納米微加工工藝,是集合微型結構、微型傳感器、微型執行器以及信號處理、控制、通信等功能于一體的完整且復雜的系統。MEMS 具有體積小、功耗低、性能好,與IC 制作工藝兼容性好等優點,在消費電子、工業控制、醫療器械、信息通信、武器裝備以及國防安全等領域中得到了越來越廣泛的應用。封裝技術決定了MEMS 器件的成本和可靠性,是MEMS 普遍實用化的基礎和實現商業化成功的關鍵因素。一方面,封裝成本制約了MEMS 商業化發展。由于MEMS 器件種類多樣,同時大多數MEMS器件的封裝都是面向特定應用,一種制造工藝和封裝工藝很難簡單的移植到其他MEMS 器件開發中,工業上MEMS 封裝沒有統一標準,這極大增加了MEMS 器件開發的技術難度和成本,一般MEMS僅封裝成本就占總成本的70% 以上。另一方面,MEMS 封裝的可靠性制約MEMS 普遍實用化。與IC不同,MEMS 一般包含精密可動微結構,MEMS 封裝不僅需要提供必要的電學和其他物理場的互聯,還需對MEMS 結構以及電連接等提供支持和保護,使之免受外部環境的干擾或破壞。封裝中面臨著結構優化、工藝條件的選擇、熱力學效應和多物理場耦合等問題。研究表明,在MEMS 系統中發生的可靠性問題50%來自電子封裝過程。

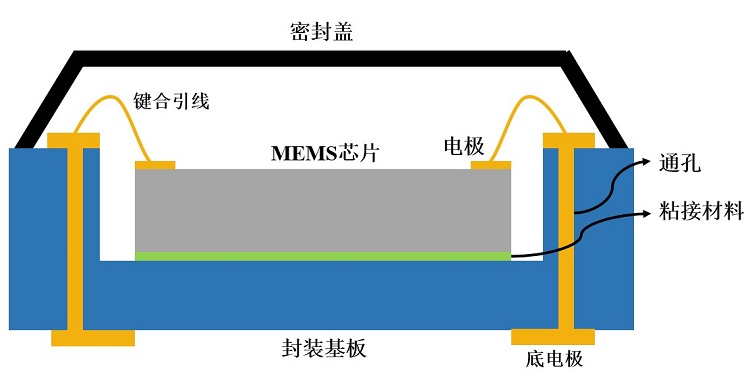

MEMS 封裝過程會引入額外的應力,嚴重影響MEMS 器件的穩定性和可靠性。封裝應力是由于MEMS 器件材料與封裝材料之間熱膨脹系數(coefficient of thermal expansion,CTE)不匹配而產生。MEMS 芯片級封裝主要用于實現芯片電學連通,同時保護芯片免受外界環境的影響。MEMS 芯片級封裝一般包括芯片粘貼、引線鍵合、封蓋和氣密焊接等關鍵基礎工藝,典型的MEMS 芯片級封裝截面示意圖如圖1 所示。

圖1 典型MEMS芯片級封裝截面示意圖

Fig.1 Schematic diagram of a typical MEMSchip scale package

研究表明,芯片粘接工藝是芯片級封裝中最主要的應力來源,MEMS 芯片襯底材料、粘接材料和封裝基板之間的材料性能不匹配,特別是MEMS 器件襯底硅與封裝基板之間材料CTE 失配從而產生較大的封裝應力。封裝應力會直接造成芯片的翹曲和變形,進而影響MEMS 器件的性能。對于一些應力敏感的MEMS 器件如壓阻傳感器、壓力傳感器來說,封裝過程產生應力直接作用于器件本身,直接影響其測量結果的準確性。對于諧振器件或者慣性器件,如MEMS 諧振器、加速度計和陀螺儀等而言,由于封裝應力引起的結構幾何形變和等效剛度變化會改變器件的諧振頻率 和品質因子(quality factor,Q),從而造成傳感器的輸出信號如刻度因子和零偏等產生漂移。當器件上的應力過大時,會導致MEMS 器件在界面區域產生裂紋、分層甚至失效,從而破壞MEMS 器件的互連,引起失效或引發長期的可靠性問題。

控制和減少封裝應力對于提高對于應力敏感的MEMS 器件如壓力傳感器、諧振器以及慣性器件的性能可靠性和長期穩定性具有重要的意義。因此,本文主要聚焦于芯片粘接工藝,分析了芯片粘接工藝中封裝應力的產生機理,同時從封裝材料、封裝工藝以及封裝結構方面詳細介紹了目前芯片粘接工藝中降低封裝應力和提高應力敏感MEMS 器件性能和穩定性的方法,并對于MEMS 器件低應力封裝技術進行了總結和展望。

1 芯片粘接工藝中應力產生機理

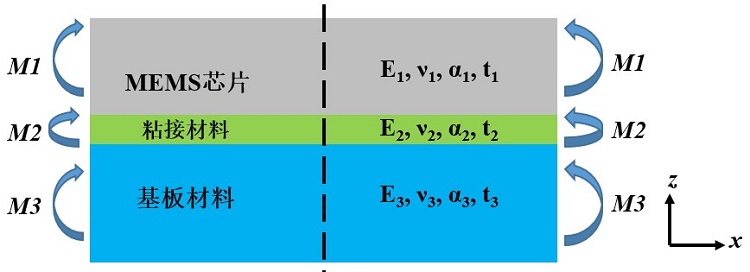

芯片粘接工藝是通過粘接材料將芯片連接到封裝基板上的工藝過程。該工藝一般分為施膠、貼片和固化3 個步驟,首先將MEMS 芯片通過粘接材料固定于封裝基板,之后加熱整體結構至固化溫度,最后冷卻至室溫即完成芯片粘接。從固化溫度冷卻到室溫的過程中,由于MEMS 襯底、粘接材料層和封裝基板之間的材料性能不匹配而產生了的殘余熱應力,導致MEMS 封裝結構發生形變。在芯片粘接過程中,MEMS 芯片、粘接材料和封裝基板典型3 層結構如圖2 所示。

圖2 芯片粘接過程中典型的3層結構

Fig.2 Typical three-layer structure in die attachment process

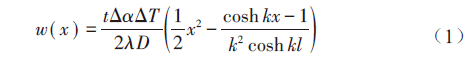

根據Suhir 理論,從純彎曲過程中彎曲力矩與彎曲曲率的關系出發,采用數值分析的方法推導出了芯片粘接過程中封裝應力的解。在此3 層結構中,每層材料的厚度和力學性能決定了整體的翹曲或撓度w( x) 如下式表示:

芯片粘接過程中的剪切應力τ0( x),可以精確地表示為:

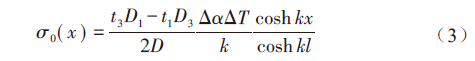

芯片粘接過程中的剝離應力σ0( x),可以精確地表示為:

其中,Ei 為第i 層材料的楊氏模量;Gi 為第i 層材料的剪切模量;vi 為第i 層材料的泊松比;αi 為第i 層材料的熱膨脹系數;ti 為第i 層材料的厚度;t 為多層結構總的厚度;Δα = α3 - α1,為芯片與封裝基板材料熱膨脹系數的差值;ΔT = To - Tref,為工作溫度To 與固化溫度Tref 的差值;

由式(1)、(2)和(3)可知,封裝熱應力與冷卻過程中固化溫度與工作溫度差值以及芯片與封裝基板材料CTE 的差值成正比,同時封裝應力與各層材料的彈性模量、泊松比以及厚度相關。

2 低應力芯片粘接

基于封裝應力產生的機理,為了降低MEMS 封裝過程中的封裝應力,目前研究主要從封裝材料、封裝工藝以及封裝結構等方面做出優化,將針對上述3個方面介紹和分析低應力芯片粘接方法。

2.1 封裝材料優化

在芯片粘接工藝中MEMS 芯片材料、粘接材料和基板材料之間物理性能的差異是封裝應力的來源。因此,封裝材料的選擇和優化有利于降低封裝應力。

2.1.1 粘接材料

常用的芯片粘接材料主要包括環氧樹脂、共晶焊料和摻金屬玻璃粘接劑等。環氧樹脂應用于芯片的低溫粘接,由于環氧樹脂導熱和導電性較差,通常在環氧樹脂中加入金屬粉末(如金和銀等)用于提高環氧樹脂的導熱性和導電性;而共晶焊料和摻金屬玻璃粘接劑主要應用于芯片的高溫粘接,適用于大功率器件,其粘接質量較好,但成本較高。表1 為部分粘接材料的物理性質,從中可以看出環氧樹脂的固化溫度低于摻銀玻璃粘接劑以及共晶焊料,采用環氧樹脂粘接材料所引起的封裝應力更小。

表1 部分粘接材料物理性質

Table 1 Physical properties of some adhesive materials

Walwadka 等研究了芯片粘接工藝中粘接材料的楊氏模量和CTE 對于封裝應力引起的芯片形變的影響。結果表明,粘接材料的CTE 對于封裝應力影響不大,粘接材料的彈性模量越小,應力越小。降低粘接材料的固化溫度和楊氏模量能明顯降低MEMS器件封裝應力。基于此,K?niger 等提出了一種基于丙烯酸酯的低溫固化、低楊氏模量以及具有高粘結強度的低應力粘接材料。該新型粘接材料楊氏模量低至0.1GPa,同時固化溫度為降至100℃ ,有效降低了MEMS 封裝應力。目前,德國的Henkel、美國的ZYMET 和EPOXY 等公司已經開發出了用于MEMS低應力封裝的環氧樹脂,低楊氏模量粘接材料已經實現商業化。然而,降低粘接材料彈性模量只適用于環氧樹脂型粘接材料,低楊氏模量的環氧樹脂中并未摻入金屬粉末,因此其導熱和導電性能很差,不適用于高可靠性封裝應用。

錫銀銅SAC錫膏 錫銀銅 SACS錫膏 錫鉍銀SnBiAg錫膏 錫鉍銀銻SnBiAgSb錫膏 錫鉍銀SnBiAgX錫膏 錫鉍SnBi錫膏 BiX 錫膏 金錫AuSn錫膏 錫銻SnSb錫膏 含鉛 SnPb錫膏 各向異性導電錫膠 微間距助焊膠

2.1.2 基板材料

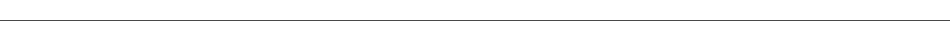

封裝基板材料與MEMS 芯片材料之間的CTE 差值是封裝應力的最主要來源,減小基板與芯片之間的CTE 的差值能有效減小封裝應力。常用MEMS 芯片材料的物理性質如表2 所示,表3 為常用的封裝基板材料物理性質參數。

表2 常用MEMS 芯片材料物理性質

Table 2 Physical properties of commonly usedMEMS chip materials

表3 常用封裝基板材料物理性質

Table 3 Physical properties of commonly usedsubstrate materials

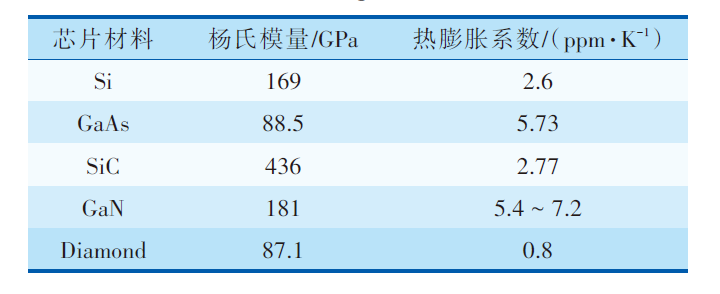

孫志國等探究了FR-4(印刷電路板)基板和Al2O3陶瓷基板在芯片粘接固化過程中MEMS 硅芯片表面的應力,結果如表4所示。結果表明采用與硅CTE 差值較小的陶瓷基板能顯著降低封裝應力。合理選擇與MEMS 芯片材料CTE 相近的封裝材料能有效降低封裝應力,然而,在實際MEMS 器件研發中,很難使得封裝基板材料和MEMS 芯片材料CTE 完美匹配,封裝應力不可避免。此外,低熱膨脹系數的封裝基板材料價格昂貴,不利于低成本MEMS 器件的商業化應用。

表4 采用不同封裝基板材料下封裝應力

Table 4 Packaging stress under different substrate materials

2.2 封裝工藝優化

芯片粘接工藝中,封裝應力主要是在固化冷卻過程中產生,優化芯片粘貼工藝能減小封裝應力。

Frutschy 等提出一種基于熱脈沖技術局部快速加熱芯片和粘接材料的方法用于降低封裝應力。通過控制熱脈沖功率和時間使得芯片和粘接材料快速達到固化溫度,由于熱傳導時間較短,此時基板的溫度相對較低,在固化降溫時,冷卻過程中基板與芯片結構之間因熱位移失配而產生的應力可相應減少。圖3為此方法與傳統熱固化工藝下芯片翹曲結果對比,可以看出,當加熱時間小于1 s 時,芯片的整體翹曲與傳統工藝方法相比降低了50%。此方法能有效降低封裝應力,但由于工藝步驟復雜和成本高昂,限制了其廣泛應用。

圖3 傳統粘接工藝和不同脈沖加熱時間粘接工藝下芯片翹曲對比

Fig.3 Comparison of chip warpage using traditional dieattachment and pulse laser heating bonding process

Walwadkar 等提出了一種熱循環固化工藝方法用于降低封裝應力。粘接材料為銀玻璃粘接劑。在完成芯片粘接后,采用熱循環(1~400℃)的方法對整體芯片結構進行熱處理,實驗結果表明封裝應力在熱循環過程中明顯下降。銀玻璃膠在熱循環下產生了應力松弛,熱循環起到了降低封裝應力的作用。然而,該方法僅適用于銀玻璃粘接材料。

2.3 封裝結構優化

優化封裝結構是降低MEMS 封裝應力中最常用的方法。優化封裝結構可以改變封裝應力的分布和傳導,進而減小應力對于MEMS 器件的影響。芯片和封裝材料之間的封裝應力主要通過粘接材料來傳遞。圖4 為仿真芯片粘接工藝中改變粘接面積下MEMS 芯片頂面的應力變化,可以看出,隨著粘接面積減小,MEMS 芯片所受到的封裝應力越小。Li 等通過減少粘接面積的方式直接降低了封裝應力對于MEMS 加速度計性能的影響,該低應力封裝方式方法已經成功應用于摩托羅拉MEMS 器件的批量封裝。

圖4 仿真芯片粘接工藝中改變粘接面積下MEMS芯片頂面的應力變化

Fig.4 Simulated stress on the top surface of the chip under different bonding areas in die attachment

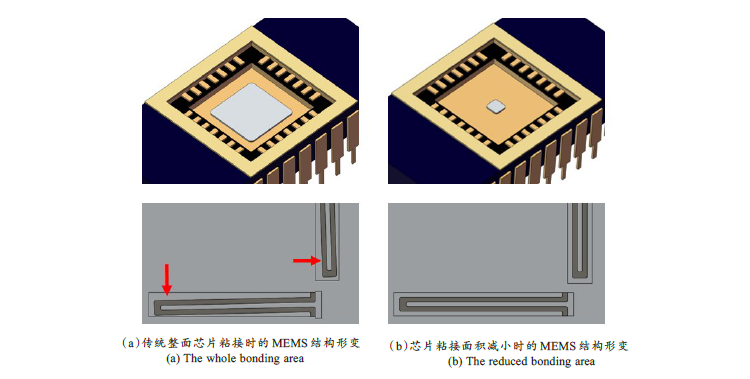

加州大學歐文分校Prikhodko 等研究了采用Au-Sn 共晶合金焊料進行芯片粘接時,粘接面積變化下封裝應力對于MEMS 陀螺儀形變和性能的影響。實驗對比了整面粘貼和較小粘接面積兩種情況下芯片粘接后陀螺儀器件的結構形變,如圖5 所示。整面粘貼結構下器件梁結構明顯發生變形,如圖5(a)所示。減小芯片粘接面積后MEMS 器件結構形變如圖5(b)所示,MEMS 陀螺儀的梁結構幾乎沒有形變。說明減小粘接面積能明顯降低MEMS 器件結構的應力和形變。同時,通過減小陀螺儀粘接面積,諧振式陀螺儀器件的頻率漂移減小至20%,有效提高了MEMS 陀螺儀的穩定性和可靠性。

圖5 不同粘接面積下由封裝應力導致MEMS器件結構形變

Fig.5 The structural deformation of MEMS devices induced by packaging stress under different bonding areas

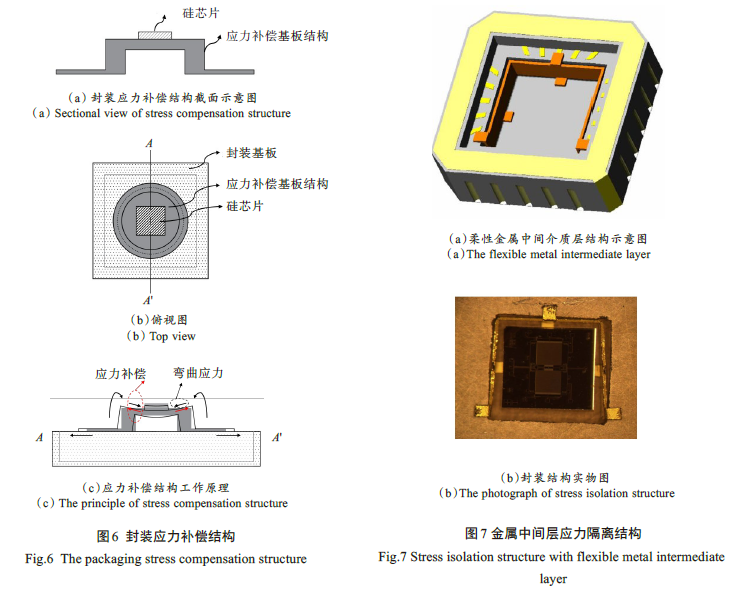

日本橫河電機公司Samejima 等提出了一種帶熱應力補償基板結構用于補償MEMS 壓力傳感器的封裝應力,如圖6 所示,其封裝結構如圖6(a)和(b)所示。該應力補償結構為帶凹腔的基板結構。其工作原理如圖6(c)所示,將硅芯片粘貼在熱應力補償結構的基板上時,當基板結構受熱膨脹時,熱應力補償結構下端受到拉應力而使上端凹陷,此結構變化會使芯片下端產生壓應力,此壓應力會抵消芯片因熱膨脹而產生的拉應力;同理,當基板受冷收縮時,熱應力補償結構下端受到壓應力,熱應力補償結構上端突起,在芯片下端產生拉應力,會補償芯片因冷收縮而產生的壓應力,從而起到降低應力的作用。采用傳統芯片粘接工藝下,由封裝應力所導致的壓力傳感器輸出誤差高達250 με/K,而采用熱應力補償結構的壓力傳感器輸出誤差降至6 με/K,該方法有效降低了封裝應力對于壓力傳感器輸出誤差的影響。

Marinis 等通過在陶瓷基板上加入柔性金屬中間介質層結構用于降低芯片粘接應力,其結構如圖7所示。中間層結構可以減少芯片與陶瓷基板之間的熱膨脹失配,起到應力隔離的作用。與傳統粘貼方式相比,加入柔性金屬中間層結構下由于應力引起的芯片翹曲降低了5 倍左右,大幅度減少了粘接過程引起的應力。

Schr?der 等提出了一種雙面引線鍵合法用于MEMS 陀螺儀低應力封裝。該方法利用雙面引線鍵合工藝替代了傳統芯片粘接工藝。MEMS 芯片是通過封裝外框引出數條金屬引線,實現電學導通的同時,將MEMS 芯片的上、下端面進行固定。該方法通過導線點固定MEMS 芯片,大幅度降低了與基板之間的粘接面積,能起到良好的應力隔離作用。采用雙面引線鍵合方式下由應力所引起的MEMS 陀螺儀芯片形變明顯減小,說明此方法能有效降低由應力引起的芯片翹曲。通過優化鍵合線的數量,該方法能減少MEMS 陀螺儀的共振模式,降低了雜模態對于MEMS 陀螺儀性能的影響。然而,此方法增加了工藝的復雜性,不利于實現大規模批量制造。

3 結論

MEMS 封裝涉及機械、材料、力學、熱物理及電子信息等多學科與多領域交叉,粘接過程中材料選擇、工藝和封裝結構的不合理都會導致封裝應力的產生。封裝應力嚴重影響對于應力敏感器件如MEMS 壓力傳感器、諧振器以及慣性器件的穩定性和可靠性。本文同時從封裝材料、封裝工藝以及封裝結構方面詳細介紹了目前芯片粘接工藝中降低封裝應力的方法,目前降低封裝應力的方法仍然存在一些局限性,低應力封裝材料只適用于特定的應用場合,封裝工藝以及結構普遍存在結構復雜,成本較高等缺點。

隨著MEMS 器件應用的不斷發展,工業中對于應力敏感的MEMS 器件的精度和穩定性要求不斷提高。低成本和通用性的低應力封裝技術仍是一個挑戰。未來降低封裝應力的手段主要集中于兩個方面,一是新型封裝材料的研發,應致力于開發通用性好的低應力粘接材料以及與MEMS 芯片材料CTE 完美匹配的封裝基板材料,才能從根本上減小封裝應力;二是封裝結構的進一步優化,主要集中于應力隔離結構和應力補償結構的開發。在此基礎上,需具體考慮不同種類MEMS 傳感器的結構和工作原理,同時兼顧封裝方法的成本和復雜性,才能提出對應的降低應力的有效方法。

作者:吳忠燁,楊尚書,吳國強

(武漢大學工業科學研究院)

深圳市福英達20年以來一直深耕于微電子與半導體封裝材料行業。致力于為業界提供先進的焊接材料和技術、優質的個性化解決方案服務與可靠的焊接材料產品。提供包括LED微間距低溫封裝錫膏錫膠、LED微間距中溫高溫封裝錫膏錫膠、LED微間距低溫高強度錫膏錫膠、倒裝芯片封裝焊料、FPC柔性模塊封裝錫膏錫膠、植球/晶圓級植球助焊劑、凸點制作錫膏、PCBA錫膏錫膠、車用功率模塊封裝錫膏錫膠、車載娛樂封裝錫膏錫膠、車用LED封裝焊料、車載MEMS封裝焊料、軌道交通用IGBT封裝錫膏錫膠、基帶芯片系統級封裝錫膏錫膠、存儲芯片高可靠封裝錫膏錫膠、射頻功率器件封裝錫膏錫膠、多次回流封裝錫膏錫膠、物聯網安全芯片封裝焊料、支付芯片系統級封裝焊料、物聯網身份識別封裝焊料、MEMS微機電系統封裝錫膏錫膠、射頻功率器件錫膏錫膠、芯片封裝錫膏錫膠、攝像頭模組封裝專用錫膠、簡化封裝工藝免洗錫膏/錫膠、高可靠性水洗錫膏、低溫高強度錫膏/錫膠、便于返修的錫膏產品、高性價比錫膏方案、高可靠高溫Au80Sn20焊料、高可靠Low alpha 高鉛封裝焊料、高可靠水洗焊料、醫療設備高可靠性封裝錫膏錫膠、醫療設備系統級封裝焊料、復雜結構激光焊接錫膏錫膠、精密結構低溫封裝焊料解決方案。以及mLED新型顯示各向異性導電膠、mLED新型顯示微間距焊接助焊膠、mLED新型顯示高強度細間距錫膠、mLED新型顯示微間距低溫焊料、mLED新型顯示微間距SAC305錫膏、SMT低溫元器件貼裝錫膠、SMT低溫元器件貼裝錫膏、SMTSAC305系列錫膏、SMT微間距助焊膠、Low α無鉛焊料、SiP水洗錫膏、SiP無鉛無銀焊料、Low α高鉛焊料、MEMS水洗激光錫膏、MEMS低溫高可靠性錫膠、MEMS低溫高可靠錫膏、MEMS多次回流焊料、MEMSAu80Sn20金錫焊膏、功率器件高鉛焊料、功率器件水洗錫膏、功率器件無鉛錫膏、功率器件Au80Sn20金錫錫膏解決方案。

返回列表

返回列表